Key Features

- Fully compatible with ANSI/ATA 878.1 Local Area Network standard for ARCNET

- Up to 4 transmit/receive pages for ARCNET packets

- Bit rates adjustable from 19 kbit/s to 10 Mbit/s (higher bit rates on request)

- Automatic packet transmission abort after EXCNAK

- Duplicate node ID detection

- Simple register-based interface

- Receive-All Mode

- Bridge function with virtual nodes

- Complete network nodelist

- Classic bus interface

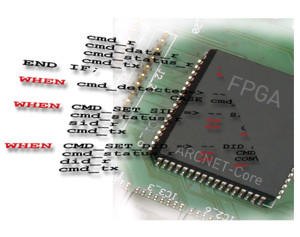

- Available for Altera and Xilinx FPGAs, may easily be ported to other FPGAs

- Easy in-field updates and upgrades

Application & Functionality

The SH IP-CORE-ARCCTRL is an IP core that implements an ARCNET network controller for use in FPGAs (Field Programmable Gate Arrays). It has been designed for and developed in VHDL. Portations exist for Altera and Xilinx FPGAs, it may be easily ported to other FPGA types.

The IP core is completely compatible to the ARCNET standard.

Due to its high flexibility the design may be used for a wide field of applications:

- One-Chip PCI-Express ARCNET card

- Simple and cost-effective node for versatile digital I/O

- Universal ARCNET-ARCNET or ARCNET-Ethernet bridge with virtual node-mapping

- Highspeed point-to-point connections

- Embedded networking

- System-On-Chip solutions

We use SH IP-CORE-ARCCTRL in our own products.