# SHIP-CORE-ARCCTRL Enhanced ARCNET Controller for FPGA-based designs

Version 02.12.2

## CONTENTS

| 1  | Revision history                                                                            | 4  |

|----|---------------------------------------------------------------------------------------------|----|

| 2  | Overview                                                                                    | 5  |

| 3  | Features                                                                                    | 5  |

|    | 3.1 Applications                                                                            | 5  |

| 4  | Host interface                                                                              | 6  |

|    | 4.1 Registers                                                                               | 6  |

|    | 4.1.1 Commands                                                                              | 8  |

|    | 4.1.1.1 Subcommands                                                                         | 11 |

|    | 4.1.2 Status registers                                                                      |    |

|    | 4.1.2.1 IRQ_STS_PAC_ITPI Register                                                           | 13 |

|    | 4.1.2.2 IRQ_STS_PAC_PS Register                                                             | 13 |

|    | 4.1.2.3 IRQ_STS_SYS Register                                                                | 13 |

|    | 4.1.3 IRQ MASK Registers                                                                    | 14 |

|    | 4.1.3.1 IRQ_MASK_PAC Register                                                               |    |

|    | 4.1.3.2 IRQ_MASK_SYS Register                                                               | 14 |

|    | 4.1.4 STS_PAGE Register                                                                     | 15 |

|    | 4.1.5 Page Queuing                                                                          | 16 |

|    | 4.2 Messages                                                                                | 16 |

| 5  | Bridge Mode                                                                                 | 19 |

| 6  | Input / Output Pins                                                                         | 20 |

|    | 6.1 System Interface                                                                        | 20 |

|    | 6.2 ARCNET Transceiver Interface                                                            | 20 |

|    | 6.3 Classic Interface                                                                       | 21 |

|    | 6.4 AXI BRAM Interface                                                                      | 21 |

| 7  | Implementation                                                                              |    |

|    | 7.1 Intel (formerly: Altera) FPGAs                                                          | 22 |

|    | 7.1.1 Development Tool                                                                      | 22 |

|    | 7.1.2 Resources                                                                             | 22 |

|    | 7.2 Xilinx FPGAs                                                                            |    |

|    | 7.2.1 Development Tool                                                                      |    |

|    | 7.2.2 Resources                                                                             |    |

| 8  | Technical background information                                                            | 23 |

| 9  | Software                                                                                    | 24 |

|    | 9.1 Hints for programmers                                                                   |    |

|    | 9.1.1 Interrupts                                                                            |    |

|    | 9.1.2 Extended timeouts                                                                     |    |

| SC | DHARD Embedded Systems GmbH Manual SH IP-CORE-ARCCTRL 2 of Version 02.12.2, Date 2020-11-06 | 27 |

|    | 9.1.3 Exa  | amples            | 25 |

|----|------------|-------------------|----|

|    |            | Initialization    |    |

|    | 9.1.3.2    | Transmit a packet | 25 |

|    | 9.1.3.3    | Receive a packet  | 26 |

| 10 | Glossary   |                   | 27 |

| 11 | Disclaimer |                   | 27 |

| 12 | References | 5                 | 27 |

| 13 | Licensing  |                   | 27 |

| 14 | Contact Ad | dress             | 27 |

# 1 Revision history

| Version    | Change                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| V. 02.12.2 | - Various message descriptions updated                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| V. 02.12.1 | - Revised Chapter 7 Implementation<br>- Changed telephone number<br>- Layout                                                                                                                                                                                                                                                                                             |  |  |  |  |

| V. 02.12   | <ul> <li>Abort after EXNAKs fixed (3.1.1 Commands, IP-core V. 0.107)</li> <li>Interrupt handling updated (9.1.1 Interrupts, IP-core V. 0.106)</li> <li>Timeout values updated (9.1.2 Extended timeouts)</li> <li>Prerequisite for feedback loop added (6.2 ARCNET Transceiver Interface)</li> <li>Emulated nodes rephrased from virtual nodes (5 Bridge Mode)</li> </ul> |  |  |  |  |

| V. 02.11   | <ul> <li>Clarification on subcommands</li> <li>Additional message descriptions</li> <li>Formatting improved</li> </ul>                                                                                                                                                                                                                                                   |  |  |  |  |

| V. 02.10   | Clarification on messages                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| V. 02.09   | - Revised descriptions of timeout commands<br>- Added new chapter 'Extended timeouts'                                                                                                                                                                                                                                                                                    |  |  |  |  |

| V. 02.08   | - Changes in description of CMD_SET_PAGE<br>- Changes in chapter 9.1.2.3 Receive a packet                                                                                                                                                                                                                                                                                |  |  |  |  |

| V. 02.07   | <ul> <li>Fixed misspelling</li> <li>Better description of demo mode</li> <li>Fixed description in AXI BRAM Interface (signal arcctrlif_data_out_o)</li> <li>Better description of IRQ_STS registers. Added addition hint for programmers.</li> </ul>                                                                                                                     |  |  |  |  |

| V. 02.06   | <ul> <li>Excluded everything about 1-wire memory device support (obsolete license method)</li> <li>Updated CMD Names and Command codes</li> <li>Updated description of CMD register</li> <li>Uniform number format of command codes and parameters</li> <li>Correction of MSG_NAME register type</li> <li>Various linguistic corrections</li> </ul>                      |  |  |  |  |

| V. 02.05   | Added Xilinx BRAM Interface                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| V. 02.04   | Editorial update and Handling of Register MSG_NAME updated (V00.97 of IP-Core)                                                                                                                                                                                                                                                                                           |  |  |  |  |

| V. 02.03   | Block diagram and pinning updated (V00.93 of IP-Core)                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| V. 02.02   | License, Software and contact information updated                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| V. 02.01   | <ul> <li>CMD_EN_TM and Recon Diagnostic Messages added (FPGA version &gt;=V00.89)</li> <li>Faster Access from Host controller (less wait states for signal wait_ext)</li> </ul>                                                                                                                                                                                          |  |  |  |  |

| V. 02.00   | CI update                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| V. 01.00   | First officially released version                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

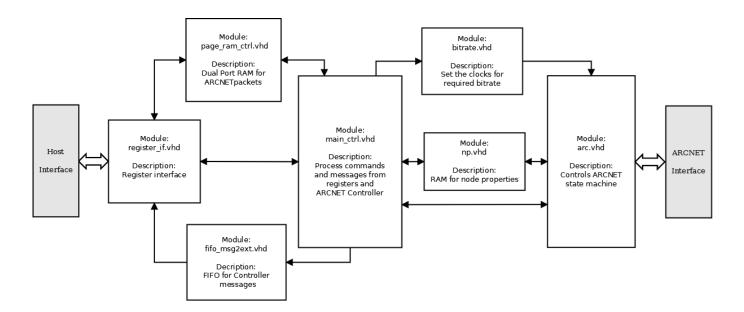

# 2 Overview

The SH IP-CORE-ARCCTRL is an ARCNET [1] controller designed for Field Programmable Gate Arrays (FPGAs). It is written in VHDL and was designed for Altera FPGAs (Stratix, Apex Cyclone and MAX10 families) and Xilinx FPGAs (Kintex 7, Spartan 3/3E, Virtex 2,4, Zynq). The design contains some Altera/Xilinx megafunctions like RAMs and FIFOs, which are clearly identified and have to be substituted when FPGAs of other vendors are used. Compared to classic "hardcoded" ICs, the SH IP-CORE-ARCCTRL offers unlimited possibilities for the users to adapt the design to their needs.

# 3 Features

- Fully compatible to ANSI/ATA 878.1 Local Area Network Standard for ARCNET

- Up to 16 transmit/receive pages for long and short ARCNET packets

- Bit rates adjustable from 19 kbit/s up to 10 Mbit/s

- Automatic packet transmission abort after EXCNAK

- Token auto-repeat

- Improved network configuration

- Enhanced diagnostic functions

- Duplicate node detection

- Simple register-based interface

- Receive-All Mode (configurable)

- Bridge function with emulated nodes (configurable)

- Complete Network Node List (configurable)

- "Classic" bus interface

- Design entirely written in VHDL, except for RAM and FIFO functions only

- May be easily adapted to other FPGA types

- In-field updates and upgrades are simple

- Future-proof

- Free license for SH IP-CORE-ARCCTRL in Demo Mode (fix node-id)

### 3.1 Applications

Due to its high flexibility the design may be used for or adapted to a wide field of applications:

- One-Chip PCI ARCNET card (a free PCI Core is available from www.opencores.org)

- Simple and cost-effective node for versatile digital I/O

- Universal ARCNET- ARCNET or ARCNET-Ethernet bridge with emulated node-mapping

- High speed point-to-point connections

- Embedded networking

- System-On-Chip solutions

# 4 Host interface

The host interface is the interface to an external or internal microcontroller. It is very similar to an ISA-bus-like interface with read, write, chip select control signals, an 8-bit data bus and a 4-bit address bus.

### 4.1 Registers

Only a few registers are required to control the SH IP-CORE-ARCCTRL.

| Name of Register | Address<br>(hex) | Read/Write | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAR              | 0                | R/W        | <ul> <li>Parameter field for CMD. Must be set prior to executing a CMD which requires a parameter.</li> <li>Additionally, this register contains the return value of any CMD_GET_xx command.</li> <li>Note: <ol> <li>A write access to this register is ignored if the previous command has not been completed.</li> <li>Writing to this register disables the interrupt temporarily. The interrupt is enabled again, when the CMD register is written to.</li> </ol> </li> </ul>                                                                               |

| CMD              | 1                | R/W        | <ul> <li>Writing to this register triggers the IP-CORE-ARCCTRL to execute the written command (see table of the commands).</li> <li>After-wards this register contains the status of the command execution:</li> <li>value 0xFF - command is still being processed other value - command execution is completed. The value equals to the code of the executed command. Note:</li> <li>1) writing to the CMD register is ignored, if previous command has not been completed.</li> <li>2) the execution status will be reported via message register.</li> </ul> |

| PAGE_DATA        | 2                | R/W        | This register is used to read and write data from and to the selected data page (see command SET_PAGE). Any access to this register will automatically increment the address pointer (see registers ADDR_L and ADDR_H). The address of the data is set by the registers ADDR_L and ADDR_L.                                                                                                                                                                                                                                                                      |

| reserved         | 3                | -          | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ADDR_L           | 4                | R/W        | Lower byte of the address that points to the data on the selected page (see command SET_PAGE). The address pointer is incremented automatically with each write or read access to the PAGE_DATA register. The command SET_PAGE resets this value to 0x04.                                                                                                                                                                                                                                                                                                       |

| ADDR_H           | 5                | R/W        | Upper byte of the address that points to the data on the selected page (see command SET_PAGE). The address pointer is incremented automatically with each write or read access to the PAGE_DATA register. The command SET_PAGE resets this value to 0x00.                                                                                                                                                                                                                                                                                                       |

| IRQ_STS_PAC_ITPI | 6                | R          | This register shows interrupts from data pages that are generated on completion of packet receipt and transmission. If enabled, each data transmission causes an interrupt. Bit 30                                                                                                                                                                                                                                                                                                                                                                              |

| Name of Register | Address<br>(hex) | Read/Write | Description                                                                                                                                                                                                                                                                                                           |

|------------------|------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                  |            | contains the page index, Bit 74 the events. See Table IRQ_STS_PAC.                                                                                                                                                                                                                                                    |

| IRQ_STS_PAC_PS   | 7                | R          | This register contains the status of the transmission of the page that generated an interrupt (see IRQ_STS_PAC_ITPI)                                                                                                                                                                                                  |

| IRQ_STS_SYS      | 8                | R          | Various events like Reconfigurations, etc. are recorded by this register. If enabled, each event causes an interrupt. See Table IRQ_STS_SYS.                                                                                                                                                                          |

| MSG_PAR          | 9                | R          | Contains a parameter field for the MSG_NAME (see MSG_NAME)                                                                                                                                                                                                                                                            |

| MSG_NAME         | A                | R/W        | The MSG_NAME register is supplied by an internal FIFO. The messages provide information on the internal status of the controller, network events and responses to CMDs (see 3.2). The message will be updated on write access. So the software needs to write any value to MSG_NAME in order to get the next message. |

| reserved         | BF               |            | reserved                                                                                                                                                                                                                                                                                                              |

### 4.1.1 Commands

Receiving a command (and if necessary a parameter) the SH IP-CORE-ARCCTRL performs the required action like setting parameters, starting packet transmission, receptions and so on. If the command requires a parameter, this parameter must be written to the PAR register beforehand. Writing a command code to the CMD register, will cause the command to be executed.

| CMD Name          | Command code | Parameter | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|--------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | (hex)        | (hex)     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                   |              | 01FF      | Sets the Node ID. Must be set prior to enabling the controller.                                                                                                                                                                                                                                                                                                                                                                                                     |

| CMD_SET_SID       | 01           |           | <u>Note:</u> In Evaluation-mode the CMD_SET_SID command is ignored, and Node ID is hard-coded to 0x0A.                                                                                                                                                                                                                                                                                                                                                              |

|                   |              | 001F      | Bits 03 set the number of FBE-NAK sequences, after which the PAC_TX_EXNAK in the IRQ_STS_SYS register will be set (EXNAK = Excessive NAKs).<br>Zero value for the bits 03 disables the transmission retries, for other values the number of retries will result in the power of 2 of the respective value (value 1 will result in 2 retries, 2 in 4 retries up to 15 resulting in 32768 retries).                                                                   |

| CMD_SET_EXNAK     | 07           |           | Bit 4 sets the EXNAK auto abort option:<br>If enabled, an ongoing packet transmission will be aborted after<br>EXNAK occurred and STS_PAC_ABORT will be issued in the<br>STS_PAGE register.<br>If disabled, the packet transmission will continue.                                                                                                                                                                                                                  |

|                   |              |           | Default after power-up or reset is 128 NAKs with auto-abort being disabled.                                                                                                                                                                                                                                                                                                                                                                                         |

| CMD_SET_BITRATE   | 08           | 0009      | Sets the ARNCET bit rate. 0 corresponds to 19 kBps, 1 to 38 kBps, 7 to 2.5 Mbps and so on up to 10 Mbps.<br><u>Note:</u> Setting the bit rate will automatically resets the ARCNET state machine, therefore it is recommended to set the bit rate directly after controller reset.                                                                                                                                                                                  |

| CMD_SET_DEBUG_LVL | 0C           | 00FF      | Defines which kind of MSGs are stored in the MSG FIFO. Default<br>value is 0x3F (all messages except for errors are disabled).<br>Bit0=1: ignore ACK, NAK messages<br>Bit1=1: ignore FBE messages<br>Bit2=1: ignore messages of the type MSG_ITT<br>Bit3=1: ignore messages of the type MSG_MY_ITT<br>Bit4=1: ignore most messages except for any kind of error<br>message<br>Bit5=1: ignore all network messages like<br>MSG_TOKENPASS_FAIL, MSG_NEXTID_FOUND etc. |

| CMD_GET_PARAM     | 29           | 1         | This command allows to read the values of controller parameters (see Table "Subcommands").<br>The value may be read from the PAR register after the command was executed.                                                                                                                                                                                                                                                                                           |

| CMD_DIS_ARC       | 37           | -         | Disables the ARCNET transmitter of the controller. Parameters will<br>not be changed. Packet transfers will be canceled. Some<br>monitoring activity will still be active.                                                                                                                                                                                                                                                                                          |

| CMD_EN_ARC        | 38           | -         | Enables the ARCNET transmitter of the controller. The bit rate and the SID must have been set beforehand. The SH IP-CORE-ARCCTRL starts joining the network.                                                                                                                                                                                                                                                                                                        |

| CMD_EN_BRDCST_RX  | 42           | -         | Enables the controller to receive Broadcast packets. Broadcasts are disabled by default.                                                                                                                                                                                                                                                                                                                                                                            |

| CMD_DIS_BRDCST_RX | 43           | -         | Disables the controller to receive Broadcast packets. Broadcasts are disabled by default.                                                                                                                                                                                                                                                                                                                                                                           |

Table: SH IP-CORE-ARCCTRL commands and parameters

<sup>&</sup>lt;sup>1</sup>One of the subcommands described in the following section

|                     | code<br>(hex) | Parameter<br>(hex) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|---------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD_RST_ARC         | 44            | -                  | Resets the internal state machines. All network activity will be<br>immediately stopped. All network-related parameters (except for the<br>bit rate) need to be set again. A minimum waiting time of 20us is<br>required, before the next read/write access.                                                                                                                                                                                                                                                                                                      |

| CMD_RST_MSG_FIFO    | 45            | -                  | The FIFO containing MSGs is being reset and all messages will be deleted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CMD_EN_TM           | 46            | -                  | Enables various features for testing an ARCNET network.<br>Par=0x01: The next transmitted packets will contain an erroneous<br>CRC<br>Par=0x02: Tokens sent to this node will be ignored. This causes a<br>reconfiguration sooner or later.                                                                                                                                                                                                                                                                                                                       |

| CMD_SET_ENHNCD_MODE | 48            | 0001               | Bit 0:<br>Enables/disables the Token Repeat function. If enabled, the token<br>pass will repeated once, if the first try has failed. If disabled, the<br>node will search for the next available node in the network as<br>defined in [1] after one token pass has failed. Default is off.<br>Bit 17 reserved for future expansions                                                                                                                                                                                                                               |

| CMD_REQ_NP_STS      | 4D            | 01FE               | Requests a status of the nodes that were detected by the controller<br>in the range from the node ID defined by the parameter to 0xFF.<br>After the request the SH IP-CORE-ARCCTRL will be incrementally<br>processing its internal node list and reporting for detected nodes<br>their node ID, status and node ID of the upper neighboring node.<br>The request will be completed after 8 nodes were reported or the<br>end of the list was reached.<br>The command is only available, if the Bridge Mode option or the<br>Network Node List option is enabled. |

| CMD_RX_ALL_EN       | 4E            | -                  | Enables the Receive-All Mode.<br>The command will be only available if the Receive-All option is<br>enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CMD_RX_ALL_DIS      | 4F            | -                  | Disables the Receive-All Mode.<br>The command will be only available if the Receive-All option is<br>enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

The timeout commands are only needed for extended timeout operation [1]. For timeout level-0, it's not necessary to change the counter values.

The optimum counter values depend on the number of nodes in the network, the bit-rate and the run-time of the signal on the network lines.

All counter values represent multiples of a given bit length. Therefore the counter value is independent from the data-rate. See also chapter 'Extended timeouts'.

Please be careful to use the same timeout settings for all nodes in the network.

| nodes be careful to dee the dame amount betangs for an nodes in the network. |    |      |                                                                                                                                                                                                                                                                               |  |

|------------------------------------------------------------------------------|----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CMD_SET_TMR_TLT_L                                                            | 10 | 00FF | Sets the lower byte of the counter for the Token Lost Timer.<br>This counter value represents multiples of 2048 bit lengths.<br>The register defaults to the standard timeout value (1025 = 840ms<br>@2.5Mbps) [1].                                                           |  |

| CMD_SET_TMR_TLT_H                                                            | 11 | 00FF | Sets the upper byte of the Token Lost Timer.                                                                                                                                                                                                                                  |  |

| CMD_SET_TMR_TIP_L                                                            | 12 | 00FF | Sets the lower byte of the counter for the <b>K-value</b> of the Identifier<br>Precedence Timer. TIP=K*(255-ID)+3us. [1]<br>The counter value represents multiples of 0.5 bit lengths.<br>The register defaults to the standard timeout value (730 = 146 us<br>@2.5Mbps) [1]. |  |

| CMD_SET_TMR_TIP_H                                                            | 13 | 00FF | Sets the upper byte of the Identifier Precedence Timer.                                                                                                                                                                                                                       |  |

| CMD_SET_TMR_TAC_L                                                            | 14 | 00FF | Sets the lower byte of the Activity Timeout Timer.<br>The counter value represents multiples of 0.5 bit lengths. The<br>register defaults to the standard timeout value (425 = 85 us<br>@2.5Mbps) [1].                                                                        |  |

| CMD_SET_TMR_TAC_H                                                            | 15 | 00FF | Sets the upper byte of the Activity Timeout Timer.                                                                                                                                                                                                                            |  |

| CMD_SET_TMR_TRP_L                                                            | 16 | 00FF | Sets the lower byte of the counter for the Response Timer.<br>This counter value represents multiples of 0.5 bit lengths.<br>The register defaults to the standard timeout value (383 = 76.6 us<br>@2.5Mbps) [1].                                                             |  |

| CMD_SET_TMR_TRP_H                                                            | 17 | 00FF | Sets the upper byte of the Response Timer                                                                                                                                                                                                                                     |  |

|                      | Command       | Parameter |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------|---------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD Name             | code<br>(hex) | (hex)     | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                      |               | Inter     | rupt Commands                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CMD_SET_IRQ_MASK_PAC | 09            | 00FF      | Enables interrupt sources. See table for IRQ_MASK_PAC                                                                                                                                                                                                                                                                                                                                                                           |

| CMD_SET_IRQ_MASK_SYS | 0A            | 00FF      | Enables interrupt sources. See table for IRQ_MASK_SYS                                                                                                                                                                                                                                                                                                                                                                           |

|                      |               | 00 FF     | Resets the IRQ_STS_SYS bits if the corresponding bit in the parameter field is set.                                                                                                                                                                                                                                                                                                                                             |

| CMD_CLEAR_IRQ_SYS    | 0B            | 00FF      | The interrupt output is set inactive, if all bits in the IRQ_STS_SYS and IRQ_STS_PAC are cleared.                                                                                                                                                                                                                                                                                                                               |

|                      | 0D            | 00 55     | Resets the IRQ_STS_PAC bits if the corresponding bit in the parameter field is set.                                                                                                                                                                                                                                                                                                                                             |

| CMD_CLEAR_IRQ_PGE    | 00            | 00FF      | The interrupt output will be disabled, if all bits in the IRQ_STS_SYS and IRQ_STS_PAC are cleared.                                                                                                                                                                                                                                                                                                                              |

|                      | <u> </u>      | PAC       | GE Commands                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                      |               |           | Sets the current page. All subsequent CMDs regarding packet transfers refer to this page. Bits 03 of the parameter field indicate the page index.                                                                                                                                                                                                                                                                               |

|                      | 18            |           | <b>Note</b> : Writing or reading to the page via the PAGE_DATA register <i>always starts</i> (after CMD_SET_PAGE) at an internal offset of 4 bytes referred to the beginning of the page. The first four bytes of the page are reserved for internal purposes for transmission. This must be taken in account, if a RAM test shall be performed                                                                                 |

| CMD SET PAGE         |               | 000F      | Preparing a packet for transmission: First select the page (CMD_SET_PAGE). Then simply write the data to the PAGE_DATA register. DID, packet length and SID (in Bridge Mode only) must have been set by the appropriate commands before starting the transmission with the EN_PAC_TX command. To make sure that a previous transmission from this page has been completed, the status of the page should be checked beforehand. |

|                      |               |           | Reading a received packet: If the information about the length, SID or DID of the received packet is necessary, the page address should be set to 0 (ADDR_L=0) after CMD_SET_PAGE. The data structure is:                                                                                                                                                                                                                       |

|                      |               |           | Address 0: STS_PAGE                                                                                                                                                                                                                                                                                                                                                                                                             |

|                      |               |           | Address 1: LSB of packet length                                                                                                                                                                                                                                                                                                                                                                                                 |

|                      |               |           | Address 2: SID                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                      |               |           | Address 3: DID                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                      |               |           | Address 4: Start of payload                                                                                                                                                                                                                                                                                                                                                                                                     |

|                      |               |           | To make sure the data is valid, the STS_PAGE register should be evaluated first. Please note, that the DID is not valid, if a broadcast packet has been received.                                                                                                                                                                                                                                                               |

|                      |               |           | Sets the Destination ID for a packet transmission to another node in the network.                                                                                                                                                                                                                                                                                                                                               |

| CMD_SET_DID          | 02            | 00FF      | 0 means the packet will be transmitted as a broadcast packet.                                                                                                                                                                                                                                                                                                                                                                   |

|                      |               |           | Refers to the page selected by the CMD_SET_PAGE command.                                                                                                                                                                                                                                                                                                                                                                        |

| CMD_SET_TX_SID       | 19            | 01FF      | Sets SID for the data packet in selected data page (5).                                                                                                                                                                                                                                                                                                                                                                         |

| CMD_SET_PAC_LEN_L    | 05            | 00FD      | Sets the lower byte of the length of a data packet to be sent. Refers to the page selected by the CMD_SET_PAGE command. <b>Note:</b> packet with lengths of 254 – 256 and > 508 are not allowed.                                                                                                                                                                                                                                |

| CMD_SET_PAC_LEN_H    | 06            | 0001      | Packet length is >= 257 byte (if set to 1), otherwise 1253<br>according to the CMD_SET_PAC_LEN_H command<br>Refers to the page selected by the CMD_SET_PAGE command.                                                                                                                                                                                                                                                            |

| CMD_EN_PAC_TX        | 35            | 000F      | Enables a packet transmission and defines the selected page as a transmit page. All required parameters like DID, LEN and packet                                                                                                                                                                                                                                                                                                |

| CMD Name            | Command<br>code<br>(hex) | Parameter<br>(hex) | Description                                                                                                                                                                                                                                                                                                                                                            |  |

|---------------------|--------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                     |                          |                    | data must have been set before executing this command. The<br>parameter field indicates the selected page. Be aware, that the<br>transmission will only take place, if an ongoing transfer has been<br>completed and no other pages had been enabled before. The<br>packets are transmitted in the same order, as they have been<br>enabled.                           |  |

| CMD_EN_PAC_RX       | 40                       | 000F               | Enables a page for receiving and defines the selected page as a receive page. The parameter field indicates the selected page. Be aware, that the reception takes place only, when an ongoing running transfer has been completed and no other pages had been enabled before. The packets are stored on the selected page in the same order as they have been enabled. |  |

| CMD_DIS_PAC_RX      | 41                       | 000F               | Disables a page from receiving. The parameter field indicates the selected page. If the page was activated before for receiving, the STS_PAGE Register will show an STS_PAC_RX_ABORT condition. Otherwise this register will only be cleared.                                                                                                                          |  |

| CMD_GET_PAGE_LEN    | 25                       | 00FF               | Gets the lower byte of the data length on the selected data page.<br>The upper byte is encoded in the page status (see Table )                                                                                                                                                                                                                                         |  |

| CMD_GET_PAGE_STS    | 27                       | 000F               | Gets the current status of a page. See table STS_PAGE.<br>The parameter field indicates the selected page. The return value<br>will be stored in the PAR Register                                                                                                                                                                                                      |  |

| CMD_ABORT_TX_PAC    | 36                       | -                  | Aborts a packet transmission. This command is executed only if the current PAC is not being transmitted.                                                                                                                                                                                                                                                               |  |

| Bridge Commands (4) |                          |                    |                                                                                                                                                                                                                                                                                                                                                                        |  |

| CMD_VN_EN_NODE      | 49                       | 01FF               | Enables an emulated node. After this command the SH IP-CORE-<br>ARCCTRL acts like an ARCNET node with the node ID given in the<br>parameter field.                                                                                                                                                                                                                     |  |

| CMD_VN_DIS_NODE     | 4A                       | 01FF               | Disables an emulated node.                                                                                                                                                                                                                                                                                                                                             |  |

| CMD_VN_EN_RX        | 4B                       | 01FF               | Enables an emulated node for receiving packets.<br>Note: To receive packets, the standard procedure for receiving<br>packets (CMD_EN_PAC_RX etc.) has to be additionally performed.                                                                                                                                                                                    |  |

| CMD_VN_DIS_RX       | 4C                       | 01FF               | Prevents an emulated node from receiving packets.<br>The emulated node will answer FBE queries by NAK.                                                                                                                                                                                                                                                                 |  |

(1) depends on the FPGA used and the applied clock frequency.

(2) '-' means "Don't Care".

(3) All timing values and bit

(3) All timing values and bit rates refer to an external clock of 40 MHz.

(4) The command is only available, if the Bridge Mode option is enabled.

#### 4.1.1.1 Subcommands

### Subcommands are used for the CMD\_GET\_PARAM commands.

Table: Subcommands for the CMD\_GET\_PARAM command

| Subcommand Names Subcommand (hex) |    | Description                                                                                                                                        |

|-----------------------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------|

| PAR_NID                           | 01 | The node ID of this node.                                                                                                                          |

| PAR_EXNAK                         | 07 | For the description see CMD_SET_EXNAK command                                                                                                      |

| PAR_BITRATE                       | 08 | The adjusted bit rate.                                                                                                                             |

| PAR_IRQ_MASK_PAC                  | 09 | See CMD_SET_IRQ_MASK_PAC command                                                                                                                   |

| PAR_IRQ_MASK_SYS                  | 0A | See CMD_SET_IRQ_MASK_SYS command                                                                                                                   |

| PAR_NEXTID                        | 39 | The node ID of the upper neighboring node (next node ID). Will be 0, if there is no neighboring node or if the network is currently reconfiguring. |

| Subcommand Names   | Subcommand<br>(hex) | Description                                                                                                                                                                                                     |  |

|--------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                    |                     | Bit 0 = 1 indicates a node in the network with the same node ID as this present node. In this case the command CMD_EN_ARC should never be executed, as duplicate node IDs will cause malfunctions in a network. |  |

|                    |                     | Bit 1= 1 means no activity on the network, i. e. no other node is active.                                                                                                                                       |  |

|                    |                     | Bit 2 = 1 means a network with only one node has been detected.                                                                                                                                                 |  |

| PAR NWRK STS       | 3A                  | Bit 3 = 1 means some tokens have been detected.                                                                                                                                                                 |  |

|                    |                     | All bits will be reset by a CMD_DIS_ARC, CMD_SET_SID or CMD_RST_ARC command.                                                                                                                                    |  |

|                    |                     | Bit 4 = 1 means the network is stable (Reconfiguration finished, regular token-passing and data traffic). The bit is valid only, if the Bridge Mode option or the Network Node List option is enabled.          |  |

|                    |                     | Bit 5 = 1 means the netmap is ready                                                                                                                                                                             |  |

| PAR_FPGA_VENDOR_ID | 40                  | Vendor of the FPGA: 0 = Altera, 1= Xilinx, 2= Actel, others for future use                                                                                                                                      |  |

|                    |                     | FPGA family:                                                                                                                                                                                                    |  |

| PAR_FPGA_FAMILY_ID | 41                  | Altera: 0 = Cyclone, 1= Stratix, 2 = Apex, 3 = Cyclone II, 4 = Cyclone IV<br>Xilinx: 0 = Spartan, 1 = Virtex                                                                                                    |  |

| PAR_PM_ID_L        | 42                  | The individual product ID (lower byte) for the customer whom the IP-Core was compiled for. 00 = unknown                                                                                                         |  |

|                    | 43                  | The individual ID (upper byte) for the customer whom the IP-Core was compiled for.                                                                                                                              |  |

| PAR_PM_ID_H        |                     | 00 = prototypes, 01 = SOHARD Embedded Systems GmbH, 02 04 = reserved, others are available on request.                                                                                                          |  |

| PAR_VER_MAJOR      | 44                  | Version, upper byte                                                                                                                                                                                             |  |

| PAR_VER_MINOR      | 45                  | Version, lower byte                                                                                                                                                                                             |  |

| PAR_NR_OF_PAGES    | 46                  | Indicates the number of TX/RX pages available. The maximum value is 16 and depends on the type of FPGA the design was compiled for.                                                                             |  |

|                    |                     | Bit 0: Message FIFO is enabled/disabled                                                                                                                                                                         |  |

|                    |                     | Bit 1: CMD_SET_TMR_xx commands enabled (if disabled the built-in default values will be used)                                                                                                                   |  |

|                    |                     | Bit 2: Network Status detection is enabled/disabled                                                                                                                                                             |  |

|                    |                     | Bit 3: Enhanced Mode functions enabled. See CMD_SET_ENHNCD_MODE command.                                                                                                                                        |  |

|                    | 47                  | Bit 4: Fast Host interface. If 1, the interface will be clocked with the external clock, otherwise with half of the external clock.                                                                             |  |

| PAR_SYS_RSRC       |                     | Bit 5: Bridge Mode. If 1, the Bridge Mode is enabled, and emulated nodes are available.                                                                                                                         |  |

|                    |                     | Bit 6: Network Node List. The complete Network Node List is available using CMD_REQ_NP_STS commands.                                                                                                            |  |

|                    |                     | Bit 7: If 1, Demo Mode is enabled. In Demo mode the CMD_SET_SID command is not being executed. This means the node ID of the SH IP-CORE-ARCCTRL is fixed to the default value 0x0A.                             |  |

|                    |                     | 1 means enabled, 0 disabled.                                                                                                                                                                                    |  |

| PAR_ENHNCD_MODE    | 48                  | Bit 0 = 1: the Token Repeat function is enabled. See<br>CMD_SET_ENHCD_FCKTS.                                                                                                                                    |  |

|                    |                     | Bits 17 = 0 (reserved)                                                                                                                                                                                          |  |

|                    |                     | Bit 0: Receive-All Mode is enabled/disabled                                                                                                                                                                     |  |

| PAR_SYS_RSRC1      | 49                  | Bits 17: reserved                                                                                                                                                                                               |  |

|                    |                     | 1 means enabled, 0 disabled.                                                                                                                                                                                    |  |

### 4.1.2 Status registers

The status registers show events that recently occurred. If enabled by the SET\_IRQ\_MASK\_PAC or SET\_IRQ\_MASK\_SYS command an event triggers an interrupt. Please note that you may not immediately see all occurred events at once and have to clear older events first, before seeing other events (see also chapter 'Hints for programmers').

| Name       | Bit | Description                                                                                                                                        |

|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Page index | 30  | The page number to which the event refers.                                                                                                         |

| PAC_TX_END | 4   | The transmission of a packet has been completed. Whether the transmission was successful or not may be retrieved via the CMD_GET_PAGE_STS command. |

| PAC_RX_END | 5   | A data packet has been received. Whether the reception was successful or not may be retrieved via the CMD_GET_PAGE_STS command.                    |

| reserved   | 67  | reserved                                                                                                                                           |

#### 4.1.2.1 IRQ\_STS\_PAC\_ITPI Register

Each bit may be reset individually by a CMD\_CLEAR\_IRQ\_PGE command, if the corresponding bit in the parameter field is set.

#### 4.1.2.2 IRQ\_STS\_PAC\_PS Register

This register contains the status of the page that is referenced in the IRQ\_STS\_PAC\_ITPI register (for details see Table STS\_PAGE Register).

| 4.1.2.3 | IRQ | STS | SYS | Register |

|---------|-----|-----|-----|----------|

|         |     |     |     |          |

| Event        | Bit | Description                                                                                                                                    |

|--------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|

| RECON        | 0   | A reconfiguration burst has been triggered by this present node.                                                                               |

| NEW_NEXT_ID  | 1   | A new upper neighboring node (next node ID) has been detected.                                                                                 |

| PAC_TX_EXNAK | 2   | All FBEs for the packet transmission of a page have been declined by NAKs for the number of times set by CMD_SET_EXNAK.                        |

| MSG_BUF_HALF | 3   | The message buffer is half full.                                                                                                               |

| MSG_ERROR    | 4   | An error or warning has been stored in the Message FIFO.                                                                                       |

| NO_ACTIVITY  | 5   | A "No Activity" condition has been detected. This usually occurs after a reconfiguration burst.                                                |

| NW_CHANGE    | 6   | The Network Node List has changed.<br>The function is available only, if the Bridge Mode option or the Network Node List<br>option is enabled. |

| reserved     | 7   | reserved                                                                                                                                       |

Each bit may be reset individually by a CMD\_CLEAR\_IRQ\_SYS command, if the corresponding bit in the parameter field is set.

### 4.1.3 IRQ MASK Registers

The interrupt mask registers enable or disable the various interrupt sources. They are controlled by the CMD\_SET\_IRQ\_MASK\_PAC / CMD\_SET\_IRQ\_MASK\_SYS commands.

4.1.3.1 IRQ\_MASK\_PAC Register

| Name       | Bit | Description                                                                                     |

|------------|-----|-------------------------------------------------------------------------------------------------|

| reserved   | 03  |                                                                                                 |

| PAC_TX_END | 4   | Enables interrupts for the following event:<br>the transmission of a packet has been completed. |

| PAC_RX_END | 5   | Enables interrupts for the following event:<br>A packet has been received.                      |

| reserved   | 67  |                                                                                                 |

### 4.1.3.2 IRQ\_MASK\_SYS Register

| Event        | Bit | Description                                                                                                                                                                                                                   |

|--------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RECON        | 0   | Enables interrupts for the following event:<br>A reconfiguration burst has been sent by this controller.                                                                                                                      |

| NEW_NEXT_ID  | 1   | Enables interrupts for the following event:<br>A new upper neighboring node has been detected                                                                                                                                 |

| PAC_TX_EXNAK | 2   | Enables interrupts for the following event:<br>All FBEs for the packet transmission of a page have been declined by NAKs for the<br>number of times set by CMD_SET_EXNAK.                                                     |

| MSG_BUF_HALF | 3   | Enables interrupts for the following event:<br>The message buffer is half-full.                                                                                                                                               |

| MSG_ERROR    | 4   | Enables interrupts for the following event:<br>Message indicating the storage of an error or warning in the Message FIFO                                                                                                      |

| NO_ACTIVITY  | 5   | Enables interrupts for the following event:<br>A "No Activity" condition has been detected. Usually occurring after a<br>reconfiguration burst.                                                                               |

| NW_CHANGE    | 6   | Enables interrupts for the following event:<br>The network has become stable or has become unstable (i. e. reconfigurations<br>occur).<br>This function is available only, if the Bridge Mode option or the Network Node List |

|              |     | option is enabled. It may be used to trigger a read-out of the Network Node List via the CMD_REQ_NP_STS command.                                                                                                              |

| reserved     | 7   |                                                                                                                                                                                                                               |

### 4.1.4 STS\_PAGE Register

After a CMD\_GET\_PAGE\_STS command the status of a page may be read from the PAR register. The table shows the possible status values. The status bits have different meanings if used as either a TX page or an RX page.

| Name            | Bit | Value (hex) | Description                                                                                                                                                                                          |

|-----------------|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAC_LEN         | 0   | 0,1         | 0 means the packet contains up to 253 data bytes,<br>1 means it contains 257 data bytes or more.                                                                                                     |

| PAGE_MODE       | 1   | 1           | The page is configured as a TX page.                                                                                                                                                                 |

| EN_PAGE         | 2   | 0,1         | If 1, the page is enabled for transmission.                                                                                                                                                          |

| STS_IDLE        | 53  | 0           | Reset value. If set, the page is waiting for being activated.                                                                                                                                        |

| STS_PAC_PENDING | 53  | 1           | The page has been activated and will be transmitted as soon the receiving node is ready for reception.                                                                                               |