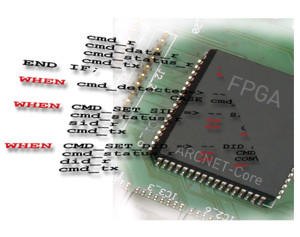

SH IP-CORE-ARCCTRL

ARCNET-Netzwerk-Controller IP-Core für FPGA-basierte Designs

Leistungsmerkmale

- Vollständig kompatibel zu ANSI/ATA 878.1, Local Area Network Standard für ARCNET

- Bis zu 4 Sende/Empfangs-Seiten für ARCNET-Pakete

- Bitraten einstellbar von 19 kbit/s bis zu 10 Mbit/s (höhere Bitraten auf Anfrage)

- Automatischer Abbruch der Paketübertragung nach EXCNAK

- Erkennung doppelt vorhandener Knoten-IDs

- Einfaches Register-Interface

- Receive-All-Modus

- Bridge-Funktion mit virtuellen Knoten

- Komplette Knotenliste des Netzwerks

- Klassische Bus-Schnittstelle

- Verfügbar für Altera- und Xilinx-FPGAs, kann leicht auf andere FPGAs portiert werden

- In-field-Updates und -Upgrades sind leicht auszuführen

Bestellinformationen

Wir bieten verschiedene Lizenzmodelle an, bitte sprechen Sie mit uns.

Einsatzgebiet

Der SH IP-CORE-ARCCTRL ist ein IP-Core, der einen ARCNET-Netzwerk-Controller zum Einsatz in FPGAs (Field-Programmable-Gate-Arrays) realisiert. Er wurde in VHDL programmiert und für Altera- und Xilinx-FPGAs entwickelt. Das Design kann leicht auf andere FPGA-Typen portiert werden.

Der IP-Core ist voll kompatibel zum ARCNET-Standard.

Wegen seiner hohen Flexibilität kann das Design in einem breiten Anwendungsfeld eingesetzt werden:

- One-Chip-PCI-Express/ARCNET-Karten

- Einfache und rentable Knoten für vielseitige digitale I/O-Anwendungen

- Universale ARCNET/ARCNET- oder ARCNET/Ethernet-Bridge mit virtuellem Node-Mapping

- Punkt-zu-Punkt-Hochleistungsverbindungen

- Embedded-Networking

- SoC-Lösungen

Wir verwenden den SH IP-CORE-ARCCTRL in unseren eigenen Produkten.